## General Description

Maxim's MX7575/MX7576 are high-speed ( $5\mu$ s/10 $\mu$ s), microprocessor ( $\mu$ P) compatible, 8-bit analog-to-digital converters (ADCs). The MX7575 provides an on-chip track/hold function that allows full-scale signals up to 50kHz (386mV/ $\mu$ s slew rate) to be acquired and digitized accurately. Both ADCs use a successive-approximation technique to achieve their fast conversions and low power dissipation. The MX7575/MX7576 operate with a +5V supply and a 1.23V external reference. They accept input voltages ranging from 0V to 2VREF.

The MX7575/MX7576 are easily interfaced to all popular 8-bit µPs through standard  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  control signals. These signals control conversion start and data access. A  $\overline{\text{BUSY}}$  signal indicates the beginning and end of a conversion. Since all the data outputs are latched and three-state buffered, the MX7575/MX7576 can be directly tied to a µP data bus or system I/O port.

Maxim also makes the **MAX165**, a plug-in replacement for the MX7575 with an internal 1.23V reference. For applications that require a differential analog input and an internal reference, the **MAX166** is recommended.

## **Applications**

Digital Signal Processing

High-Speed Data Acquisition

Telecommunications

Audio Systems

High-Speed Servo Loops

Low-Power Data Loggers

# \_Features <sup>(75)</sup>

- ♦ Fast Conversion Time: 5µs (MX7575) 10µs (MX7576)

- ♦ Built-In Track/Hold Function (MX7575)

- ♦ Low Total Unadjusted Error (±1LSB max)

- ♦ 50kHz Full-Power Signal Bandwidth (MX7575)

- ♦ Single +5V Supply Operation

- ♦ 8-Bit µP Interface

- ♦ 100ns Data-Access Time

- ♦ Low Power: 15mW

- ♦ Small-Footprint Packages

## Ordering Information

| PART             | TEMP. RANGE    | PIN-PACKAGE    | INL<br>(LSB) |

|------------------|----------------|----------------|--------------|

| <b>MX7575</b> JN | 0°C to +70°C   | 18 Plastic DIP | ±1           |

| MX7575KN         | 0°C to +70°C   | 18 Plastic DIP | ±1/2         |

| MX7575JCWN       | 0°C to +70°C   | 18 Wide SO     | ±1           |

| MX7575KCWN       | 0°C to +70°C   | 18 Wide SO     | ±1/2         |

| MX7575JP         | 0°C to +70°C   | 20 PLCC        | ±1           |

| MX7575KP         | 0°C to +70°C   | 20 PLCC        | ±1/2         |

| MX7575J/D        | 0°C to +70°C   | Dice*          | ±1           |

| MX7575AQ         | -25°C to +85°C | 18 CERDIP**    | ±1           |

| MX7575BQ         | -25°C to +85°C | 18 CERDIP**    | ±1/2         |

#### Ordering Information continued at end of data sheet.

- \* Contact factory for dice specifications.

- \*\* Contact factory for availability.

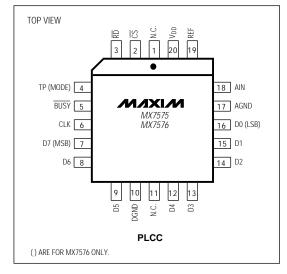

## Pin Configurations \_

#### TOP VIEW CS 18] V<sub>DD</sub> RD NAXIM 17 REF MX7575 TP (MODE) 3 16 AIN MX7576 15 AGND BLISY CLK 14 D0 (LSB) 13 D1 D7 (MSB) 12 D2 D6 D5 11 D3 10 D4 DGND 9 DIP/SO () ARE FOR MX7576 ONLY Pin Configurations continued at end of data sheet.

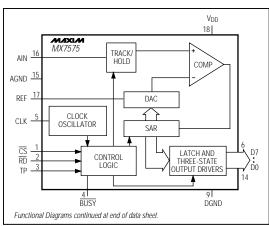

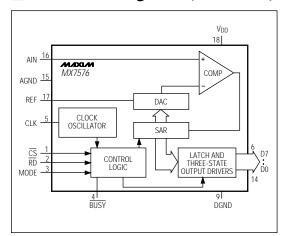

## \_Functional Diagrams

MIXIM

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com. or phone 1-800-998-8800

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to AGND        | 0.3V, +7V                    |

|--------------------------------|------------------------------|

| V <sub>DD</sub> to DGND        | 0.3V, +7V                    |

| AGND to DGND                   | 0.3V, V <sub>DD</sub> + 0.3V |

| Digital Input Voltage to DGND  |                              |

| (CS, RD, TP, MODE)             | 0.3V, V <sub>DD</sub> + 0.3V |

| Digital Output Voltage to DGND |                              |

| (BUSY, D0-D7)                  |                              |

| CLK Input Voltage to DGND      |                              |

| REF to AGND                    |                              |

| AIN to AGND                    | 0.3V, V <sub>DD</sub> + 0.3V |

|                                |                              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ |                |

|-----------------------------------------------------|----------------|

| Plastic DIP (derate 11.11mW/°C above +7             | 0°C)889mW      |

| Wide SO (derate 9.52mW/°C above +70°C               | C)762mW        |

| CERDIP (derate 10.53mW/°C above +70°                | Ć)842mW        |

| PLCC (derate 10.00mW/°C above +70°C)                | 800mW          |

| Operating Temperature Ranges                        |                |

| MX757_J/K                                           | 0°C to +70°C   |

| MX757_A/B                                           | 25°C to +85°C  |

| MX757_JE/KE                                         | 40°C to +85°C  |

| MX757_S/T                                           | 55°C to +125°C |

| Storage Temperature Range                           | 65°C to +160°C |

| Lead Temperature (soldering, 10sec)                 | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5V; V_{REF} = 1.23V; AGND = DGND = 0V; f_{CLK} = 4MHz external for MX7575; f_{CLK} = 2MHz external for MX7576; f_{CLK} = 2MHz external f_$

| PARAMETER                      | SYMBOL                   | CON                                     | IDITIONS                             | MIN    | TYP  | MAX               | UNITS  |  |

|--------------------------------|--------------------------|-----------------------------------------|--------------------------------------|--------|------|-------------------|--------|--|

| ACCURACY                       |                          |                                         |                                      |        |      |                   |        |  |

| Resolution                     |                          |                                         |                                      | 8      |      |                   | Bits   |  |

| Total Upadiusted From          | TUE                      | MX757_K/B/T                             |                                      |        |      | ±1                | LSB    |  |

| Total Unadjusted Error         | TUE                      | MX757_J/A/S                             |                                      | ±2 LSB |      | LSB               |        |  |

| Relative Accuracy              | Accuracy INL MX757_K/B/T |                                         |                                      |        | ±1/2 | LSB               |        |  |

| Relative Accuracy              | IINL                     | MX757_J/A/S                             |                                      |        |      | ±1                | LSD    |  |

| No-Missing-Codes Resolution    |                          |                                         |                                      | 8      |      |                   | Bits   |  |

| Full-Scale Error               |                          |                                         |                                      |        |      | ±1                | LSB    |  |

| Full-Scale Tempco              |                          |                                         |                                      |        | ±5   |                   | ppm/°C |  |

| Offset Error (Note 1)          |                          |                                         |                                      |        |      | ±1/2              | LSB    |  |

| Offset Tempco                  |                          |                                         |                                      |        | ±5   |                   | ppm/°C |  |

| ANALOG INPUT                   | •                        |                                         |                                      |        |      |                   | •      |  |

| Voltage Range                  |                          | 1LSB = 2V <sub>REF</sub> /256           |                                      | 0      |      | 2V <sub>REF</sub> | V      |  |

| DC Input Impedance             |                          |                                         |                                      | 10     |      |                   | MΩ     |  |

| Slew Rate, Tracking            |                          | MX7575                                  |                                      |        |      | 0.386             | V/µs   |  |

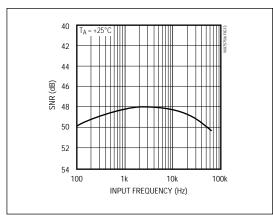

| Signal-to-Noise Ratio (Note 2) | SNR                      | MX7575, V <sub>IN</sub> = 2.46          | V <sub>p-p</sub> at 10kHz, Figure 13 | 45     |      |                   | dB     |  |

| REFERENCE INPUT                | •                        |                                         |                                      |        |      |                   |        |  |

| Reference Voltage              | V <sub>REF</sub>         | ±5% variation for sp                    | ecified performance                  |        | 1.23 |                   | V      |  |

| Reference Current              | I <sub>REF</sub>         |                                         |                                      |        |      | 500               | μΑ     |  |

| LOGIC INPUTS CS, RD, MODE      | •                        |                                         |                                      |        |      |                   | •      |  |

| Input Low Voltage              | V <sub>INL</sub>         |                                         |                                      |        |      | 0.8               | V      |  |

| Input High Voltage             | VINH                     |                                         |                                      | 2.4    |      |                   | V      |  |

| Input Current                  | l                        | $T_A = +25^{\circ}C$                    |                                      |        |      | ±1                |        |  |

| input Current                  | I <sub>IN</sub>          | V <sub>IN</sub> = 0V or V <sub>DD</sub> | $T_A = T_{MIN}$ to $T_{MAX}$         |        |      | ±10               | μA     |  |

| Input Capacitance (Note 2)     | CIN                      |                                         |                                      |        |      | 10                | pF     |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

(VDD = +5V; VREF = 1.23V; AGND = DGND = 0V; fCLK = 4MHz external for MX7575; fCLK = 2MHz external for MX7576;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                     | SYMBOL           | CONDITIO                                                      | MIN                          | TYP | MAX | UNITS     |     |  |

|-----------------------------------------------|------------------|---------------------------------------------------------------|------------------------------|-----|-----|-----------|-----|--|

| CLOCK                                         | 1                |                                                               | '                            |     |     |           |     |  |

| Input Low Voltage                             | V <sub>INL</sub> |                                                               |                              |     |     | 0.8       | V   |  |

| Input High Voltage                            | VINH             |                                                               |                              | 2.4 |     |           | V   |  |

| Input Law Current                             | 1                | V <sub>IN</sub> = 0V                                          | MX757_J/A/K/B                |     |     | 700       |     |  |

| Input Low Current                             | I <sub>INL</sub> | VIV = OA                                                      | MX757_S/T                    |     |     | 800       | μΑ  |  |

| Input High Current                            |                  | \/\/aa                                                        | MX757_J/A/K/B                |     |     | 700       |     |  |

| Input High Current                            | linh             | VIN = VDD                                                     | MX757_S/T                    |     |     | 800       | μΑ  |  |

| LOGIC OUTPUTS (D0-D7, BUS                     | <del>\</del> Y)  |                                                               |                              |     |     |           |     |  |

| Output Low Voltage                            | V <sub>OL</sub>  | I <sub>SINK</sub> = 1.6mA                                     |                              |     |     | 0.4       | V   |  |

| Output High Voltage                           | V <sub>OH</sub>  | ISOURCE = 40µA                                                |                              | 4.0 |     |           | V   |  |

| Floating State Leakage Current                |                  | Volit = 0V to Von, D0-D7                                      | T <sub>A</sub> = +25°C       |     |     | ±1        | ^   |  |

| Floating State Leakage Current                |                  | VOUT = ON 10 ADD' DO-D1                                       | $T_A = T_{MIN}$ to $T_{MAX}$ |     |     | ±10       | μA  |  |

| Floating State Output<br>Capacitance (Note 2) |                  | D0-D7                                                         |                              |     |     | 10        | pF  |  |

| CONVERSION TIME (Note 3)                      |                  |                                                               | I                            |     |     |           | l   |  |

| Conversion Time with                          |                  | MX7575: f <sub>CLK</sub> = 4MHz                               |                              |     | 5   |           | HE  |  |

| External Clock                                |                  | MX7576: f <sub>CLK</sub> = 2MHz                               |                              |     | 10  |           | μs  |  |

| Conversion Time with                          |                  | Using recommended clock components: R <sub>CLK</sub> = 100kΩ, | MX7575                       | 5   |     | 15        | μs  |  |

| Internal Clock                                |                  | $C_{CLK} = 100052$ ,<br>$C_{CLK} = 100pF$ ;<br>$T_A = +25$ °C | MX7576                       | 10  |     | 30        | μs  |  |

| POWER REQUIREMENTS (Not                       | e 4)             |                                                               |                              |     |     |           | •   |  |

| Supply Voltage                                | $V_{DD}$         | ±5% for specified performance                                 |                              |     | 5   |           | V   |  |

| Supply Current                                | IDD              | MX757_J/A/K/B                                                 |                              |     | 3   | 6         | mA  |  |

|                                               | .50              | MX757_S/T                                                     |                              |     |     | 7         |     |  |

| Power Dissipation                             |                  |                                                               |                              |     | 15  |           | mW  |  |

| Power-Supply Rejection                        |                  | $4.75V < V_{DD} < 5.25V$                                      |                              |     |     | $\pm 1/4$ | LSB |  |

Note 1: Offset Error is measured with respect to an ideal first-code transition that occurs at 1/2LSB.

For MX7575  $\overline{CS} = \overline{RD} = \overline{BUSY} = \text{high};$ For MX7576  $\overline{CS} = \overline{RD} = \overline{BUSY} = \text{MODE} = \text{high}.$

Note 2: Sample tested at +25°C to ensure compliance.

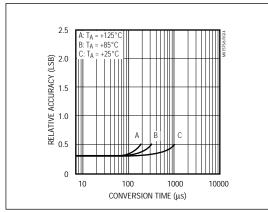

Note 3: Accuracy may degrade at conversion times other than those specified.

Note 4: Power-supply current is measured when MX7575/MX7576 are inactive, i.e.:

# **TIMING CHARACTERISTICS (Note 5)**

$(V_{DD} = +5V, V_{REF} = 1.23V, AGND = DGND = 0V.)$

|                             |                |            | T <sub>A</sub> = +25°C |     | T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |     |     |     |       |

|-----------------------------|----------------|------------|------------------------|-----|-------------------------------------------------------|-----|-----|-----|-------|

| PARAMETER                   | SYMBOL         | CONDITIONS | Α                      | LL  | J/K/A/B                                               |     | S/T |     | UNITS |

|                             |                |            | MIN                    | MAX | MIN                                                   | MAX | MIN | MAX | 1     |

| CS to RD Setup Time         | t <sub>1</sub> |            | 0                      |     | 0                                                     |     | 0   |     | ns    |

| RD to BUSY Propagation Time | t <sub>2</sub> |            |                        | 100 |                                                       | 100 |     | 120 | ns    |

| Data-Access Time after RD   | t <sub>3</sub> | (Note 6)   |                        | 100 |                                                       | 100 |     | 120 | ns    |

| RD Pulse Width              | t <sub>4</sub> |            | 100                    |     | 100                                                   |     | 120 |     | ns    |

| CS to RD Hold Time          | t <sub>5</sub> |            | 0                      |     | 0                                                     |     | 0   |     | ns    |

| Data-Access Time after BUSY | t <sub>6</sub> | (Note 6)   |                        | 80  |                                                       | 80  |     | 100 | ns    |

| Data-Hold Time              | t7             | (Note 7)   | 10                     | 80  | 10                                                    | 80  | 10  | 100 | ns    |

| BUSY to CS Delay            | tg             |            | 0                      |     | 0                                                     |     | 0   |     | ns    |

**Note 5:** Timing specifications are sample tested at +25°C to ensure compliance. All input control signals are specified with  $t_r = t_f = 20$ ns (10% to 90% of +5V) and timed from a voltage level of 1.6V.

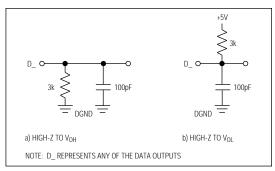

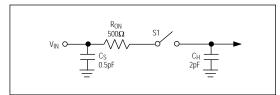

Note 6: t<sub>3</sub> and t<sub>6</sub> are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V.

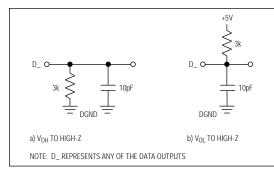

Note 7: t7 is defined as the time required for the data lines to change 0.5V when loaded with the circuits of Figure 2.

# Pin Description

| P      | IN    | NAME             | FUNCTION                                                                                                                                                              |

|--------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP/SO | PLCC  | NAME             | FUNCTION                                                                                                                                                              |

| 1      | 2     | CS               | Chip Select Input. $\overline{\text{CS}}$ must be low for the device to be selected or to recognize the $\overline{\text{RD}}$ input.                                 |

| 2      | 3     | RD               | Read Input. $\overline{\text{RD}}$ must be low to access data. $\overline{\text{RD}}$ is also used to start conversions. See the<br>Microprocessor Interface section. |

| 3      | 4     | TP<br>(MX7575)   | Test Point. Connect to V <sub>DD</sub> .                                                                                                                              |

| 3      | 4     | MODE<br>(MX7576) | Mode Input. MODE = low puts the ADC into its asynchronous conversion mode. MODE has to be tied high for the synchronous conversion mode and the ROM interface mode.   |

| 4      | 5     | BUSY             | BUSY Output. BUSY going low indicates the start of a conversion. BUSY going high indicates the end of a conversion.                                                   |

| 5      | 6     | CLK              | External Clock Input/Internal Oscillator Pin for frequency setting RC components.                                                                                     |

| 6      | 7     | D7               | Three-State Data Output, bit 7 (MSB)                                                                                                                                  |

| 7, 8   | 8, 9  | D6, D5           | Three-State Data Outputs, bits 6 and 5                                                                                                                                |

| 9      | 10    | DGND             | Digital Ground                                                                                                                                                        |

| 10–13  | 12–15 | D4-D1            | Three-State Data Outputs, bits 4–1                                                                                                                                    |

| 14     | 16    | D0               | Three-State Data Output, bit 0 (LSB)                                                                                                                                  |

| 15     | 17    | AGND             | Analog Ground                                                                                                                                                         |

| 16     | 18    | AIN              | Analog Input. 0V to 2V <sub>REF</sub> input range.                                                                                                                    |

| 17     | 19    | REF              | Reference Input. +1.23V nominal.                                                                                                                                      |

| 18     | 20    | $V_{DD}$         | Power-Supply Voltage. +5V nominal.                                                                                                                                    |

| _      | 1, 11 | N.C.             | No Connect                                                                                                                                                            |

4

Figure 1. Load Circuits for Data-Access Time Test

## **Detailed Description**

#### **Converter Operation**

The MX7575 and MX7576 use the successive-approximation technique to convert an unknown analog input voltage to an 8-bit digital output code (see Functional Diagrams). The MX7575 samples the input voltage on an internal capacitor once (at the beginning of the conversion), while the MX7576 samples the input signal eight times during the conversion (see MX7575 Track/Hold and MX7576 Analog Input sections). The internal DAC is initially set to half scale, and the comparator determines whether the input signal is larger than or smaller than half scale. If it is larger than half scale, the DAC MSB is kept. But if it is smaller, the MSB is dropped. At the end of each comparison phase, the SAR (successive-approximation register) stores the results of the previous decision and determines the next trial bit. This information is then loaded into the DAC after each decision. As the conversion proceeds, the analog input is approximated more closely by comparing it to the combination of the previous DAC bits and a new DAC trial bit. After eight comparison cycles, the eight bits stored in the SAR are latched into the output latches. At the end of the conversion, the BUSY signal goes high, and the data in the output latches is ready for microprocessor (µP) access. Furthermore, the DAC is reset to half scale in preparation for the next

#### Microprocessor Interface

The  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  logic inputs are used to initiate conversions and to access data from the devices. The MX7575 and MX7576 have two common interface modes: slow-memory interface mode and ROM interface mode. In addition, the MX7576 has an asynchronous conversion mode (MODE pin = low) where continuous conversions

Figure 2. Load Circuits for Data-Hold Time Test

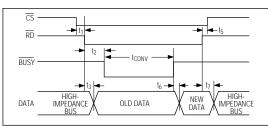

are performed. In the slow-memory interface mode,  $\overline{CS}$  and  $\overline{RD}$  are taken low to start a conversion and they remain low until the conversion ends, at which time the conversion result is latched. This mode is designed for  $\mu Ps$  that can be forced into a wait state. In the ROM interface mode, however, the  $\mu P$  is not forced into a wait state. A conversion is started by taking  $\overline{CS}$  and  $\overline{RD}$  low, and data from the previous conversion is read. At the end of the most recent conversion, the  $\mu P$  executes a read instruction and starts another conversion.

For the MX7575, TP should be hard-wired to  $V_{DD}$  to ensure proper operation of the device. Spurious signals may occur on TP, or excessive currents may be drawn from  $V_{DD}$  if TP is left open or tied to a voltage other than  $V_{DD}$ .

## Slow-Memory Mode

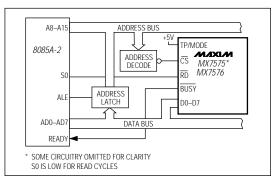

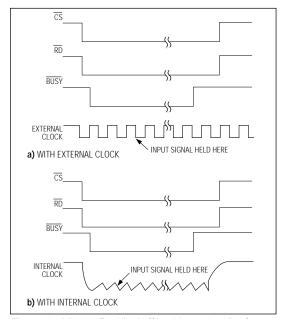

Figure 3 shows the timing diagram for slow-memory interface mode. This is used with µPs that have a waitstate capability of at least 10µs (such as the 8085A), where a read instruction is extended to accommodate slow-memory devices. A conversion is started by executing a memory read to the device (taking CS and RD low). The BUSY signal (which is connected to the μP READY input) then goes low and forces the µP into a wait state. The MX7575 track/hold, which had been tracking the analog input signal, holds the signal on the third falling clock edge after RD goes low (Figure 12). The MX7576, however, samples the analog input eight times during a conversion (once before each comparator decision). At the end of the conversion, BUSY returns high, the output latches and buffers are updated with the new conversion result, and the µP completes the memory read by acquiring this new data

The fast conversion time of the MX7575/MX7576 ensures that the  $\mu P$  is not forced into a wait state for an excessive amount of time. Faster versions of many  $\mu Ps,$

Figure 3. Slow-Memory Interface Timing Diagram

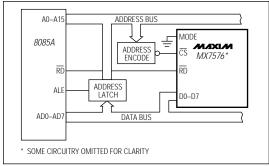

Figure 4. MX7575/MX7576 to 8085A-2 Slow-Memory Interface

including the 8085A-2, test the status of the READY input immediately after the start of an instruction cycle. Therefore, if the MX7575/MX7576 are to be effective in placing the  $\mu P$  in a wait state, their  $\overline{BUSY}$  output should go low very early in the cycle. When using the 8085A-2, the earliest possible indication of an upcoming read operation is provided by the S0 status signal. Thus, S0, which is low for a read cycle, should be connected to the  $\overline{RD}$  input of the MX7575/MX7576. Figure 4 shows the connection diagram for the 8085A-2 to the MX7575/MX7576 in slow-memory interface mode.

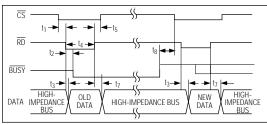

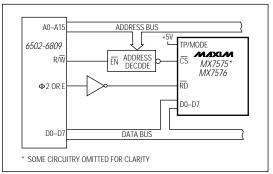

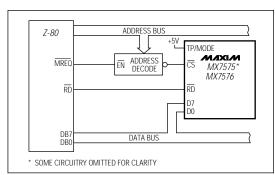

#### ROM Interface Mode

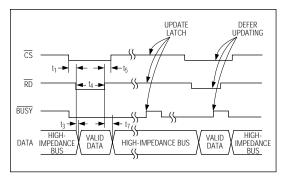

Figure 5 shows the timing diagram for ROM interface mode. In this mode, the  $\mu P$  does not need to be placed in a wait state. A conversion is started with a read instruction (RD and CS go low), and old data is accessed. The BUSY signal then goes low to indicate the start of a conversion. As before, the MX7575 track/hold acquires the signal on the third falling clock edge after RD goes low, while the MX7576 samples it eight times during a conversion. At the end of a conversion (BUSY going high), another read instruction always accesses the new data and normally starts a second conversion. However, if RD and CS go low within one

Figure 5. ROM Interface Timing Diagram

Figure 6. MX7575/MX7576 to 6502/6809 ROM Interface

external clock period of  $\overline{BUSY}$  going high, then the second conversion is not started. Furthermore, for correct operation in this mode,  $\overline{RD}$  and  $\overline{CS}$  should not go low before  $\overline{BUSY}$  returns high.

Figures 6 and 7 show the connection diagrams for interfacing the MX7575/MX7576 in the ROM interface mode. Figure 6 shows the connection diagram for the 6502/6809  $\mu$ Ps, and Figure 7 shows the connections for the Z-80.

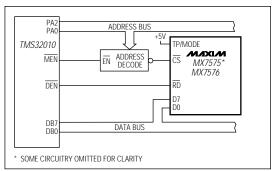

Due to their fast interface timing, the MX7575/MX7576 will interface to the TMS32010 running at up to 18MHz. Figure 8 shows the connection diagram for the TMS32010. In this example, the MX7575/MX7576 are mapped as a port address. A conversion is initiated by using an IN A and a PA instruction, and the conversion result is placed in the TMS32010 accumulator.

## Asynchronous Conversion Mode (MX7576)

Tying the MODE pin low places the MX7576 into a continuous conversion mode. The RD and CS inputs are only used for reading data from the converter. Figure 9 shows the timing diagram for this mode of operation, and Figure 10 shows the connection diagram for the 8085A. In this mode, the MX7576 looks like a ROM to

Figure 7. MX7575/MX7576 to Z-80 ROM Interface

Figure 8. MX7575/MX7576 to TMS32010 ROM Interface

the  $\mu P,$  in that data can be accessed independently of the clock. The output latches are normally updated on the rising edge of BUSY. But if  $\overline{CS}$  and  $\overline{RD}$  are low when  $\overline{BUSY}$  goes high, the data latches are not updated until one of these inputs returns high. Additionally, the MX7576 stops converting and  $\overline{BUSY}$  stays high until  $\overline{RD}$  or  $\overline{CS}$  goes high. This mode of operation allows a simple interface to the  $\mu P.$

## Processor Interface for Signal Acquisition (MX7575)

In many applications, it is necessary to sample the input signal at exactly equal intervals to minimize errors due to sampling uncertainty or jitter. In order to achieve this objective with the previously discussed interfaces, the user must match software delays or count the number of elapsed clock cycles. This becomes difficult in interrupt-driven systems where the uncertainty in interrupt servicing delays is another complicating factor.

The solution is to use a real-time clock to control the start of a conversion. This should be synchronous with

Figure 9. MX7576 Asynchronous Conversion Mode Timing Diagram

Figure 10. MX7576 to 8085A Asynchronous Conversion Mode Interface

the CLK input to the ADC (both should be derived from the same source), because the sampling instants occur three clock cycles after  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  go low. Therefore, the sampling instants occur at exactly equal intervals if the conversions are started at equal intervals. In this scheme, the output data is fed into a FIFO latch, which allows the  $\mu\text{P}$  to access data at its own rate. This guarantees that data is not read from the ADC in the middle of a conversion. If data is read from the ADC during a conversion, the conversion in progress may be disturbed, but the accessed data that belonged to the previous conversion will be correct.

The track/hold starts holding the input on the third falling edge of the clock after  $\overline{CS}$  and  $\overline{RD}$  go low. If  $\overline{CS}$  and  $\overline{RD}$  go low within 20ns of a falling clock edge, the ADC may or may not consider this falling edge as the first of the three edges that determine the sampling instant. Therefore, the  $\overline{CS}$  and  $\overline{RD}$  should not be allowed to go low within this period when sampling accuracy is required.

#### MX7575 Track/Hold

The track/hold consists of a sampling capacitor and a switch to capture the input signal. The simplified diagram of this block is shown in Figure 11. At the beginning of the conversion, switch S1 is closed, and the input signal is tracked. The input signal is held (switch S1 opens) on the third falling edge of clock after  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  go low (Figure 12). This allows a minimum of two clock cycles for the input capacitor to be charged to the input voltage through the switch resistance. The time required for the hold capacitor to settle to  $\pm 1/4 \text{LSB}$  is typically 7ns. Therefore, the input signal is allowed ample time to settle before it is acquired by the track/hold. When a conversion ends, switch S1 closes, and the input signal is tracked.

The track/hold is capable of acquiring signals with slew rates of up to 386mV/µs (or equivalently a 50kHz sine wave with 2.46Vp-p amplitude). Figure 13 shows the signal-to-noise ratio (SNR) versus input frequency for the ADC. The SNR plot is generated at a sampling rate of 200kHz using sinusoidal inputs with a peak-to-peak amplitude of 2.46V. The reconstructed sine wave is passed through a 50kHz 8th-order Chebychev filter. The improvement in SNR at high frequencies is due to the filter cutoff.

The switching nature of the analog input results in transient currents that charge the input capacitance of the track/hold. Keep the driving source impedance low (below  $2k\Omega$ ), so that the settling characteristics of the track/hold are not degraded. A low driving impedance also minimizes undesirable noise pickup and reduces DC errors caused by transient currents at the analog input. As with any ADC, it is important to keep external sources of noise to a minimum during a conversion. Therefore, keep the data bus as quiet as possible during a conversion, especially when the track/hold is making the transition to the hold mode.

For conversion times that are significantly longer than 5µs, the device's accuracy may degrade slightly, as shown in Figure 14. This degradation is due to the charge that is lost from the hold capacitor in the presence of small on-chip leakage currents.

Figure 11. Equivalent Input Circuit

#### **MX7576 Analog Input**

The MX7576 analog input can also be modeled with the switch and capacitor as shown in Figure 11. However, unlike the MX7575, the MX7576 samples the input voltage eight times during a conversion (once before each comparator decision). Therefore, the precautions that apply to the MX7575 also apply to the MX7576. These include minimizing the analog source impedance and reducing noise coupling from the digital circuitry during a conversion, especially near a sampling instant.

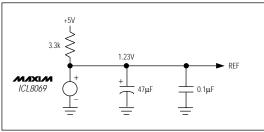

#### Reference Input

The high speed of this ADC can be partially attributed to the "inverted voltage output" topology of the DAC that it uses. This topology provides low offset and gain errors and fast settling times. The input current to the DAC, however, is not constant. During a conversion, as different DAC codes are tried, the DC impedance of the DAC can vary between  $6k\Omega$  and  $18k\Omega$ . Furthermore, when the DAC codes change, small amounts of transient current are drawn from the reference input. These characteristics require a low DC and AC driving impedance for the reference circuitry to minimize conversion errors.

Figure 15 shows the reference circuitry recommended to drive the reference input of the MX7575/MX7576.

Figure 12. MX7575 Track/Hold (Slow-Memory Interface) Timing Diagrams

Figure 13. MX7575 SNR vs. Input Frequency

Figure 14. MX7575 Accuracy vs. Conversion Time

Figure 15. External Reference Circuit

The decoupling capacitors are necessary to provide a low AC source impedance.

#### Internal/External Clock

The MX7575/MX7576 can be run with either an externally applied clock or their internal clock. In either case, the signal appearing at the clock pin is internally divided by two to provide an internal clock signal that is relatively insensitive to the input clock duty cycle. Therefore, a single conversion takes 20 input clock cycles, which corresponds to 10 internal clock cycles.

#### Internal Clock

The internal oscillator frequency is set by an external capacitor,  $C_{CLK}$ , and an external resistor,  $R_{CLK}$ , which are connected as shown in Figure 16a. During a conversion, a sawtooth waveform is generated on the CLK pin by charging  $C_{CLK}$  through  $R_{CLK}$  and discharging it through an internal switch. At the end of a conversion, the internal oscillator is shut down by clamping the CLK pin to  $V_{DD}$  through an internal switch. The circuit for the internal oscillator can easily be overdriven with an external clock source.

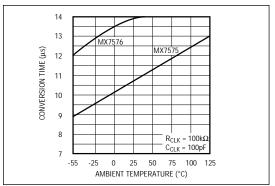

The internal oscillator provides a convenient clock source for the MX7575. Figure 17 shows typical conversion times versus temperature for the recommended R<sub>CLK</sub> and C<sub>CLK</sub> combination. Due to process variations, the oscillation frequency for this R<sub>CLK</sub>/C<sub>CLK</sub> combination may vary by as much as  $\pm 50\%$  from the nominal value shown in Figure 17. Therefore, an external clock should be used in the following situations:

- Applications that require the conversion time to be within 50% of the minimum conversion time for the specified accuracy (5µs MX7575/10µs MX7576).

- Applications in which time-related software constraints cannot accommodate conversion-time differences that may occur from unit to unit or over temperature for a given device.

#### External Clock

The CLK input of the MX7575/MX7576 may be driven directly by a 74HC or 4000B series buffer (e.g., 4049), or by an LS TTL output with a  $5.6k\Omega$  pull-up resistor. At the end of a conversion, the device ignores the clock input and disables its internal clock signal. Therefore, the external clock may continue to run between conversions without being disabled. The duty cycle of the external clock may vary from 30% to 70%. As discussed previously, in order to maintain accuracy, clock rates significantly lower than the data sheet limits (4MHz for MX7575 and 2MHz for MX7576) should not be used

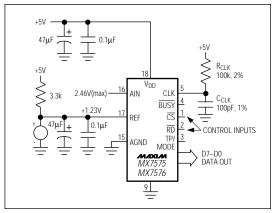

Figure 16a. Unipolar Configuration

# **Typical Applications**

## **Unipolar Operation**

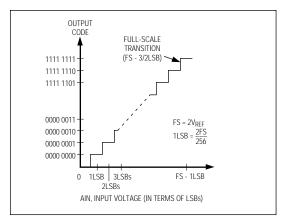

Figure 16a shows the analog circuit connections for unipolar operation, and Figure 16b shows the nominal transfer characteristic for unipolar operation. Since the offset and full-scale errors of the MX7575/MX7576 are very small, it is not necessary to null these errors in most cases. If calibration is required, follow the steps in the sections below.

#### Offset Adjust

The offset error can be adjusted by using the offset trim capability of an op amp (when it is used as a voltage follower) to drive the analog input, AIN. The op amp should have a common-mode input range that includes 0V. Set its initial input to 4.8mV (1/2LSB), while varying its offset until the ADC output code flickers between 0000 0000 and 0000 0001.

#### Full-Scale Adjustment

Make the full-scale adjustment by forcing the analog input, AIN, to 2.445V (FS - 3/2LSB). Then vary the reference input voltage until the ADC output code flickers between 1111 1110 and 1111 1111.

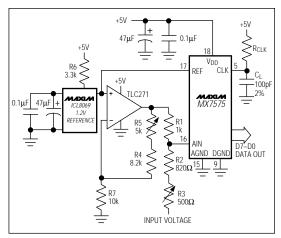

#### **Bipolar Operation**

Figure 18a shows an example of the circuit connection for bipolar operation, and Figure 18b shows the nominal transfer characteristic for bipolar operation. The output code provided by the MX7575 is offset binary. The analog input range for this circuit is  $\pm 2.46V$  (1LSB = 19.22mV), even though the voltage appearing at AIN is in the 0V to 2.46V range. In most cases, the MX7575 is

Figure 16b. Nominal Transfer Characteristic for Unipolar Operation

accurate enough that calibration will not be necessary. If calibration is not needed, resistors R1–R7 should have a 0.1% tolerance, with R4 and R5 replaced by one  $10k\Omega$  resistor, and R2 and R3 with one  $1k\Omega$  resistor. If calibration is required, follow the steps in the sections below.

#### Offset Adjust

Adjust the offset error by applying an analog input voltage of 2.43V (+FS - 3/2LSB). Then adjust resistor R5 until the output code flickers between 1111 1110 and 1111 1111.

#### Full-Scale Adjust

Null the full-scale error by applying an analog input voltage of -2.45V (-FS + 1/2LSB). Then adjust resistor R3 until the output code flickers between 0000 0000 and 0000 0001.

Figure 17. Typical Conversion Times vs. Temperature Using Internal Clock

Figure 18a. MX7575 Bipolar Configuration

## OUTPUT CODE 111...111 111...110 100...010 100...001 -1/2LSB 100...000 FS -1LSB 011...111 1/2LSB 011...110 $FS = 2V_{REF}$ 000...001 $1LSB = \frac{2FS}{256}$ 000...000

Figure 18b. Nominal Transfer Characteristic for Bipolar Operation

# \_Applications Information

#### Noise

To minimize noise coupling, keep both the input signal lead to AIN and the signal return lead from AGND as short as possible. If this is not possible, a shielded cable or a twisted-pair transmission line is recommended. Additionally, potential differences between the ADC ground and the signal-source ground should be minimized, since these voltage differences appear as errors superimposed on the input signal. To minimize system noise pickup, keep the driving source resistance below  $2k\Omega$ .

#### **Proper Layout**

For PC board layouts, take care to keep digital lines well separated from any analog lines. Establish a single-point, analog ground (separate from the digital system ground) near the MX7575/MX7576. This analog ground point should be connected to the digital system ground through a single-track connection only. Any supply or reference bypass capacitors, analog input filter capacitors, or input signal shielding should be returned to the analog ground point.

## \_Functional Diagrams (continued)

# \_Pin Configurations (continued)

# \_Ordering Information (continued)

| PART             | TEMP. RANGE     | PIN-PACKAGE    | INL<br>(LSB) |

|------------------|-----------------|----------------|--------------|

| MX7575JEWN       | -40°C to +85°C  | 18 Wide SO     | ±1           |

| MX7575KEWN       | -40°C to +85°C  | 18 Wide SO     | ±1/2         |

| MX7575JEQP       | -40°C to +85°C  | 20 PLCC        | ±1           |

| MX7575KEQP       | -40°C to +85°C  | 20 PLCC        | ±1/2         |

| MX7575SQ         | -55°C to +125°C | 18 CERDIP**    | ±1           |

| MX7575TQ         | -55°C to +125°C | 18 CERDIP**    | ±1/2         |

| <b>MX7576</b> JN | 0°C to +70°C    | 18 Plastic DIP | ±1           |

| MX7576KN         | 0°C to +70°C    | 18 Plastic DIP | ±1/2         |

| MX7576JCWN       | 0°C to +70°C    | 18 Wide SO     | ±1           |

| MX7576KCWN       | 0°C to +70°C    | 18 Wide SO     | ±1/2         |

| MX7576JP         | 0°C to +70°C    | 20 PLCC        | ±1           |

| MX7576KP         | 0°C to +70°C    | 20 PLCC        | ±1/2         |

| MX7576J/D        | 0°C to +70°C    | Dice*          | ±1           |

| MX7576AQ         | -25°C to +85°C  | 18 CERDIP**    | ±1           |

| MX7576BQ         | -25°C to +85°C  | 18 CERDIP**    | ±1/2         |

| MX7576JEWN       | -40°C to +85°C  | 18 Wide SO     | ±1           |

| MX7576KEWN       | -40°C to +85°C  | 18 Wide SO     | ±1/2         |

| MX7576JEQP       | -40°C to +85°C  | 20 PLCC        | ±1           |

| MX7576KEQP       | -40°C to +85°C  | 20 PLCC        | ±1/2         |

| MX7576SQ         | -55°C to +125°C | 18 CERDIP**    | ±1           |

| MX7576TQ         | -55°C to +125°C | 18 CERDIP**    | ±1/2         |

<sup>\*</sup> Contact factory for dice specifications.

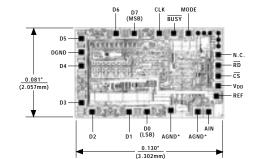

# \_Chip Topographies

# D6 D7 CLK N.C. D5 DGND D4 PR RD C5 V0D REF D2 D1 D0 AGND AGND AGND AGND (3.302mm)

MX7575

\*The two AGND pads must both be used (bonded together).

TRANSISTOR COUNT: 768 SUBSTRATE CONNECTED TO VDD

MX7576

\*The two AGND pads must both be used (bonded together).

TRANSISTOR COUNT: 768 SUBSTRATE CONNECTED TO VDD

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

2 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1996 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

<sup>\*\*</sup> Contact factory for availability.